Halka Sayıcı (Ring Counter)

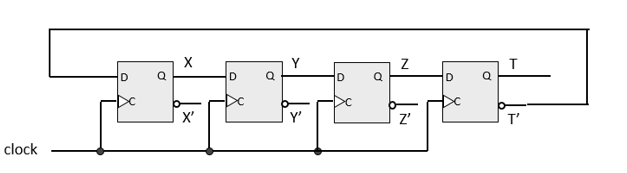

Bir halka sayıcı aslında bir binary-decimal kod çözücüdür. Sayıcı çıkışlarında girişindeki binary değerin kodu çözülerek ilgili decimal çıkış 1 yapılacaktır. Sayma işleminin her bir biti için bir flip-flop kullanılmalıdır.

Bir halka sayıcı aslında bir binary-decimal kod çözücüdür. Sayıcı çıkışlarında girişindeki binary değerin kodu çözülerek ilgili decimal çıkış 1 yapılacaktır. Sayma işleminin her bir biti için bir flip-flop kullanılmalıdır.

Devrede flip-flop'ların girişleri önceki flip-flop

çıkışlarına bağlanmıştır. Kurma ve silme girişi ile en düşük değerli flip-flop

1 değerine kurulurken diğer tüm flip-flop'lar sıfırlanır. Gelen tetikleme

sinyali ile bir sonraki flip-flop girişinde 1 görüleceğinden, çıkış 1'e

çekilecektir.

|

clock

|

X

|

Y

|

Z

|

T

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

2

|

0

|

0

|

1

|

0

|

3

|

0

|

0

|

0

|

1

|

module ring_counter(Q,Clock,Resetn);

input Clock,Resetn;

output [3:0] Q;

reg [3:0] Q;

always @(posedge Clock or negedge Resetn)

if(!Resetn)

Q <= 4'b1000;

else

Q <= {Q[0],Q[3:1]};

//Q[3]<=Q[0];

//Q[2]<=Q[3];

//Q[1]<=Q[2];

//Q[0]<=Q[1];

endmodule

Johnson Sayıcı (Johnson

Counter)

Johnson sayıcısı veya diğer adıyla dalgalı halka sayıcısı, senkron sayıcısının bir başka şeklidir. Yapısı halka sayıcısına benzer, fakat son flip-flop’tan birinci flip-flop’a yapılan geri besleme farklı yerlerden alınmıştır. Son flip-flop’un Q değil çıkışının, ilk flip-flop’un girişine bağlanmasıyla bir Johnson sayıcı devresi elde edilir.

Johnson sayıcısı veya diğer adıyla dalgalı halka sayıcısı, senkron sayıcısının bir başka şeklidir. Yapısı halka sayıcısına benzer, fakat son flip-flop’tan birinci flip-flop’a yapılan geri besleme farklı yerlerden alınmıştır. Son flip-flop’un Q değil çıkışının, ilk flip-flop’un girişine bağlanmasıyla bir Johnson sayıcı devresi elde edilir.

Ayrıca halka sayıcısındaki 1. flip-flop’u

ilk anda set ve diğerleri reset edilmişken, Johnson sayıcısında ilk anda tüm

flip-flop’lar resetlenir. Yani tüm flip-flop çıkışları ilk anda 0’dır. Saymanın

yeniden başlaması için sistemin tekrar resetlenmesi gerekir. Başlangıçta bütün flip-flop çıkışları 0’dır.

Gelen ilk tetikleme darbesi ile en düşük değerli biti taşıyan flip-flop

girişindeki 1 çıkışın 1’e çekilmesini sağlayacaktır. Gelen her tetikleme

sinyali ile birlikte 1 en yüksek değerli bite kadar seri olarak kaydırılacaktır.

En yüksek değerli biti taşıyan flip-flop çıkışının 1 olması ile birlikte Q

çıkışı 0’a çekilecek ve en düşük değerli biti taşıyan flip-flop girişinde 0

görülecektir. Bundan sonra gelen her tetikleme sinyalinde çıkışlarda sırasıyla 0

görülecektir. Bu işlem en yüksek değerli biti taşıyan flip-flop çıkışında 0

görünceye kadar devam edecektir. Devre bu durumdan sonra başlangıç adımlarına

geri dönecektir.

clock

|

X

|

Y

|

Z

|

T

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

2

|

1

|

1

|

0

|

0

|

3

|

1

|

1

|

1

|

0

|

4

|

1

|

1

|

1

|

1

|

5

|

0

|

1

|

1

|

1

|

6

|

0

|

0

|

1

|

1

|

7

|

0

|

0

|

0

|

1

|

module johnson_counter(X,Y,Z,T,clock,Resetn);

input clock,Resetn;

output X,Y,Z,T;

reg X,Y,Z,T;

always @(posedge clock or negedge Resetn)

if(!Resetn)

{X,Y,Z,T} <= 4'b0000;

else X <= ~T;

Y <= X;

Z <= Y;

T <= Z;

endmodule

Yükselen Kenar Algılayıcı (Rising Edge Detector)

module rising_edge_detector (outputs, signal_in, clk);

input signal_in, clk;

output outputs;

wire outputs;

reg signal_d;

always @ (posedge clk)

begin

signal_d <= signal_in;

end

assign outputs = (~signal_d) & signal_in;

endmodule

Düşen Kenar Algılayıcı (Falling Edge Detector)

module falling_edge_detector (outputs, signal_in, clk);

input signal_in, clk;

output outputs;

wire outputs;

reg signal_d;

always @ (posedge clk)

begin

signal_d <= signal_in;

end

assign outputs = (~signal_in) & signal_d;

endmodule

Sonlu Durum

Makineleri (Finite State Machine(FSM))

Devre

tasarımı durum dizi elemanlarının ardışık eylemlerine bağlı olduğu zaman, bir

sonlu durum makinesi (FSM) oluşturulabilir.

FSM devre tasarımının kullanıldığı alanlar:

1. Sekans Algılayıcılar

2. İlginç Sayacılar

3. Trafik Işık Kontrolü

4. Veri-Yolu Kontrolü

5. Aygıt Arabirim Denetleyicisi

Tüm durum makineleri genel geri bildirim yapıya

sahiptir. Kombinasyonel mantık devresini Next-State

Logic uygular. Makinenin sonraki durum (next state) mevcut durumu (current

state) ve diğer girişlerden oluşur. Memory(State Register)

mevcut durumunu(current state) durum saklayıcıda tutar.

Moore modelinde çıkış sadece şimdiki durumun bir fonksiyonudur.

Çıkışlar bir saat yardımıyla eş zamanlanırlar.

next_state(t)

= h(current_state(t), inputs(t))

outputs =

g(current_state(t))

Mealy

Durum Makinesi (Mealy State Machine)

Mealy modelinde çıkış hem şimdiki durum hem de

girişin bir fonksiyonudur. Çıkışlar girişler saat döngüsü (clock cycle) boyunca

değişebilir.

Bir Mealy modeli devreyi eş zamanlamak için

girişlerin saat ile eşzamanlı olması ve çıkışların da daima bir saat kenarından

hemen önce örneklenmesi gerekmektedir.

next_state(t)

= h(current_state(t), inputs(t))

FSM Verilog HDL kodu üç

ana blok içerir:

1. Durum Kodlama (State

Encoding)

2. Kombinasyonel Blok

(Combinational Block)

3. Ardışıl Blok

(Sequential Block)

Durum Kodlama (State Encoding)

Birçok şifreleme şekli

bulunmaktadır. Bunlardan bazısı listelenmektedir:

1. Binary(İkili) Kodlama

2. Bir Sıcak(One Hot)

Kodlama

3. Bir Soğuk(One Cold)

Kodlama

4. Gri(Gray) Kodlama

5. Johnson Kodlama

//Bir Sıcak Kodlama(One Hot Encoding) parameter [4:0] IDLE = 5'b00001; parameter [4:0] S0 = 5'b00010; parameter [4:0] S1 = 5'b00100; parameter [4:0] S2 = 5'b01000; parameter [4:0] S3 = 5'b10000;

//Bir Soğuk Kodlama(One Cold Encoding) parameter [4:0] IDLE = 5'b11110; parameter [4:0] S0 = 5'b11101; parameter [4:0] S1 = 5'b11011; parameter [4:0] S2 = 5'b10111; parameter [4:0] S3 = 5'b01111;

//İkili Kodlama(Binary Encoding) parameter [2:0] IDLE = 3'b000; parameter [2:0] S0 = 3'b001; parameter [2:0] S1 = 3'b010; parameter [2:0] S2 = 3'b011; parameter [2:0] S3 = 3'b100;

//Gri Kodlama(Gray Encoding) parameter [2:0] IDLE = 3'b000; parameter [2:0] S0 = 3'b001; parameter [2:0] S1 = 3'b011; parameter [2:0] S2 = 3'b010; parameter [2:0] S3 = 3'b110;

//Johnson Kodlama(Johnson Encoding) parameter [2:0] IDLE = 3'b000; parameter [2:0] S0 = 3'b100; parameter [2:0] S1 = 3'b110; parameter [2:0] S2 = 3'b111; parameter [2:0] S3 = 3'b011; parameter [2:0] S3 = 3'b001;

Verilog HDL FSM Minimum İskeleti (FSM Minimum Skeleton)

module mod_name (outputs, inputs);

input inputs;

output outputs;

parameter size = sizes;

reg [size-1: 0] current_state;

reg [size-1: 0] next_state;

// Durumlar dahil edilir.

`define state_0 2'b00

`define state_1 2'b01

always @ (current_state or the_inputs) //Next State Logic

begin

// Next-State denklemi için if veya case yapısı tanımlanır.

// Atama işlemleri yapılır.

end

always @ (negedge reset or posedge clk) //State Resgister (Memory)

begin

if (reset == 1'b0) current_state <= state_0;

else current_state <= next_state;

end

//Output atamaları

endmodule

Sekans

Algılayıcı (Sequence Detector)

Ardışık iki tane 0 ya da 1 içeren sekans

algılayıcı tasarlansın.

|

| Sekans Algılayıcı Devre Simülasyonu |

module seq_detect (out_bit, clock, reset, in_bit);

input clock, reset, in_bit;

output out_bit;

reg [2:0] state_reg, next_state;

// State declaration

parameter reset_state = 3'b000;

parameter read_1_zero = 3'b001;

parameter read_1_one = 3'b010;

parameter read_2_zero = 3'b011;

parameter read_2_one = 3'b100;

// state register

always @ (posedge clock or posedge reset)

if (reset == 1)

state_reg <= reset_state;

else

state_reg <= next_state;

// next-state logic

always @ (state_reg or in_bit)

case (state_reg)

reset_state:

if (in_bit == 0)

next_state = read_1_zero;

else

next_state = read_1_one;

read_1_zero:

if (in_bit == 0)

next_state = read_2_zero;

else

next_state = read_1_one;

read_2_zero:

if (in_bit == 0)

next_state = read_2_zero;

else

next_state = read_1_one;

read_1_one:

if (in_bit == 0)

next_state = read_1_zero;

else

next_state = read_2_one;

read_2_one:

if (in_bit == 0)

next_state = read_1_zero;

else

next_state = read_2_one;

default: next_state = reset_state;

endcase

//always blok da kullanılabilir çıkış için

assign out_bit = ((state_reg == read_2_zero) || (state_reg == read_2_one)) ? 1 : 0;

endmodule

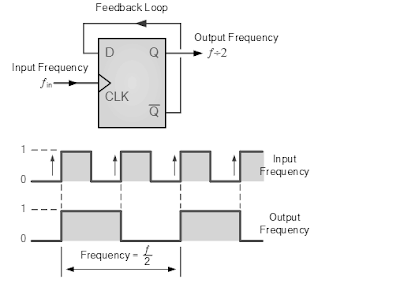

Frekans Bölücü (Frekans Divider)

Yukarı ve aşağı sayıcıların zaman

diyagramlarına bakıldığı zaman her FF'nin giriş sinyal frekansını 2'ye bölme özelliği

gösterdiğini görülebilir. clock 16 Hz ise FF1' in Q çıkışındaki

frekans 8 Hz, FF2'nin Q çıkışındaki frekans 4 Hz, FF3'nin

Q çıkışındaki frekans 2 Hz, FF4'ün Q çıkışındaki frekans ise 1 Hz

dir. Genel olarak n bitlik bir binary sayıcının çıkış frekansı;

Fout = Fclock/2n dir.

Frekans bölücü tasarımında 50 MHz Frekansı Duty

Cycle %50 iken 1 KHz frekansa ayarlansın.

module frequency_divider(clk_out,clk,rst);

input clk,rst;

output clk_out;

reg clk_out;

reg [14:0] counter; //2^15

always @(posedge clk or negedge rst)

if(!rst)

begin

counter <= 15'd0;

clk_out <= 1'b0;

end

else

begin

if(counter==15'd25000)

begin

counter <= 15'd0;

clk_out <= ~clk_out;

end

else

begin

counter <= counter+1;

//clk_out <= clk_out;

end

end

endmodule

Bir sonraki yazımda görüşmek üzere...