Ardışıl Devre Modelleme (Sequential

Circuit Modeling)

Ardışıl devreler sadece always bloğu kullanılarak modellenir. Ardışıl devre modelleme always bloğundaki

hassasiyet listesindeki kenar hassasiyetli elemanlar kullanarak yapılır. Bazen ardışıl

devreler için bloklamayan(nonblocking) atamalarda kullanılabilir.

Latch ve Flip Flop

Ardışıl devre modellemede kullanılan Latchlerde bazı problemler yaşanır. Bunlar:

1. Latch'in hangi anda enable yapılacağı bilinmelidir.

2. Latch disable duruma getirilebilmelidir.

3. Kompleks devrelerde latchlerin zamanlamasını kontrol etmek oldukça zordur.

Bu problemlerin iki yeni eleman ile çözülmesi mümkündür:

Saat, belleğe yazılacak zamanı bildirir.

Flip Flop ise, kesin olarak belirlenen zamanda

belleğe yazma işlemini gerçekleştirmeyi sağlar.

Bu iki eleman birlikte kullanılırsa, bellek

zamanlaması problemini göz ardı ederek devre tasarlanabilir. Saat çıkışı sürekli olarak belirli bir periyot ile

0 ve 1 arasında değişen özel bir devre elemanıdır.

R-S

Flip Flop

NAND veya NOR kapılı RS

Flip Flop’larda sakıncalı durum haricinde çıkışlar birbirinin tamamlayıcısı durumundadır.

Bu tür Flip Flop’lar asenkrondur. Girişler

değiştiği anda çıkışlar da değişmektedir.

Flip-Flop Devre Diyagramı

Flip-Flop Uyarım Tablosu

S

|

R

|

Q(n+1)

|

Q(n+1)’

|

Durum

|

0

|

0

|

Q(n)

|

Q(n)’

|

Hafıza

|

0

|

1

|

0

|

1

|

Reset

|

1

|

0

|

1

|

0

|

Set

|

1

|

1

|

1

|

1

|

İstenmeyen

|

R=0, S=0 durumunda Q(n) hafızadadır.

R=0, S=1 durumunda 2. kapının çıkışı 0 olacağından 1. kapının çıkışı 1 olur.

R=1, S=0 durumunda

1. kapının çıkışı 0 olur. Çünkü NOR kapısı girişlerinden en az birisi 1 olduğunda

çıkışı 0 olur.

R=1, S=1 durumunda her

iki çıkışta 0 olacağından istenmeyen bir durumdur ve kullanılmaz.

Tetiklemeli

R-S Flip-Flop

Bu Flip Flop türü, senkron çalışır. Girişlerin değişmesi,

çıkışlara hemen aktarılmaz. Bir zamanlama işaretine gereksinim vardır.

Flip-Flop Devre Diyagramı

Flip-Flop Uyarım Tablosu

CP

|

S

|

R

|

Q(n+1)

|

Q(n+1)’

|

Durum

|

↑

|

0

|

0

|

Q(n)

|

Q(n)’

|

Hafıza

|

↑

|

0

|

1

|

0

|

1

|

Reset

|

↑

|

1

|

0

|

1

|

0

|

Set

|

↑

|

1

|

1

|

1

|

1

|

İstenmeyen

|

↓

|

x

|

x

|

Q(n)

|

Q(n)’

|

Hafıza

|

J-K

Flip-Flop

R-S Flip Flop’un geliştirilmiş şeklidir. J ve K

girişleri, S ve R girişleri gibi davranmaktadır. R-S Flip Flop’taki sakıncalı durum

ortadan kalkmıştır. J ve K girişlerinin 1 olması durumunda (tetikleme sinyali

dahilinde) çıkış bir önceki konumun tersi olacaktır.

Flip-Flop Devre Diyagramı

CP

|

J

|

K

|

Q(n+1)

|

Q(n+1)’

|

Durum

|

↑

|

0

|

0

|

Q(n)

|

Q(n)’

|

Hafıza

|

↑

|

0

|

1

|

0

|

1

|

Reset

|

↑

|

1

|

0

|

1

|

0

|

Set

|

↑

|

1

|

1

|

Q(n)’

|

Q(n)

|

Toggle

|

↓

|

x

|

x

|

Q(n)

|

Q(n)’

|

Hafıza

|

module JK_FlipFlop(Q, J, K, Clock)

input J, K, Clock;

output Q;

reg Q;

always@(posedge Clock)

Q=(J&~Q) | (~K&Q); //Q+=JQ'+K'Q

endmodule

T (Toggle) Flip-Flop

T girişine 1 uygulandığı sürece, gelen tetikleme

işaretine bağlı olarak devrenin çıkışı bir önceki çıkışın tersidir.

Flip-Flop Devre Diyagramı

Flip-Flop Uyarım Tablosu

CP

|

T

|

Q(n+1)

|

Q(n+1)’

|

Durum

|

↑

|

0

|

Q(n)

|

Q(n)’

|

Hafıza

|

↑

|

1

|

Q(n)’

|

Q(n)

|

Toggle

|

↓

|

1

|

Q(n)

|

Q(n)'

|

Hafıza

|

module T_FlipFlop(Q, T, Clock)

input T, Clock;

output Q;

reg Q;

always@(posedge Clock)

Q=T^Q; //Q=T XOR Q

endmodule

D Tipi Flip-Flop

Kullanılan inverter nedeniyle RS FF’daki sakıncalı

durum ortadan kalkmış olur. Bu haliyle

D tipi FF hafıza devrelerinde kullanılan 1 bitlik temel saklayıcıdır.

Flip-Flop Uyarım Tablosu

CP

|

D

|

Q(n+1)

|

Q(n+1)’

|

Durum

|

↑

|

0

|

0

|

1

|

Reset

|

↑

|

1

|

1

|

0

|

Set

|

↓

|

x

|

Q(n)

|

Q(n)’

|

Hafıza

|

module D_Lacth(Q, D, Clock)

input D, Clock;

output Q;

reg Q;

always@(D or Clock)

if(Clock)

Q=D;

endmodule

module D_FlipFlop(Q, D, Clock)

input D, Clock;

output Q;

reg Q;

always@(posedge Clock)

Q=D; //Q'=D

endmodule

Flip Flop Dönüşümleri

İki adet Flip Flop verilsin ve bu Flip Flop’ların

birini ve mantık kapılarını kullanarak diğer Flip Flop tasarlanabilir. Bu tasarım için Flip Flop’lar XY ve ZT olsun. ZT Flip Flop'u ve mantık kapılarını

kullanarak XY Flip Flop'u tasarlansın. Bunun için ilk olarak çıktıların olası

birleşimlerini bulup, bu birleşimler için Flip Flopların girdilerini içeren

birleşik uyarım tablosu oluşturulur. Z ve T fonksiyonlarını Q(n), X ve

Y türünden ifade edilmelidir. Bunun için gerekirse karnaugh haritası da çıkarılabilir.

Son olarak da ZT Flip Flop'unun girişlerine Z ve T fonksiyonlarının

gerçekleşmeleri bağlanır.

J-K Flip Flop'un S-R FlipFlop'a

Dönüşümü

J-K Flip

Flop harici olarak bağlanmaktadır ve J-K Flip Flop kombinasyonel devrenin çıkışı olacaktır. Bu sebeple J-K Flip Flop değerleri, S-R Flip Flop ve Q(n) cinsinden elde

edilmesi gerekir. S=1 ve R=1 olduğu durumlarda çıkışa izin verilmez ve geçersiz

kabul edilir.

Flip-Flop Uyarım Tablosu

S

|

R

|

Q(n)

|

Q(n+1)

|

J

|

K

|

0

|

0

|

0

|

0

|

0

|

X

|

0

|

0

|

1

|

1

|

X

|

0

|

0

|

1

|

0

|

0

|

0

|

X

|

0

|

1

|

1

|

0

|

X

|

1

|

1

|

0

|

0

|

1

|

1

|

X

|

1

|

0

|

1

|

1

|

X

|

0

|

1

|

1

|

İstenmeyen

|

Geçersiz

|

||

1

|

1

|

İstenmeyen

|

Geçersiz

|

||

Flip-Flop Karnaugh Haritası

J-K Flip-Flop'un T Tipi

Flip-Flop'a Dönüşümü

Flip-Flop Uyarım Tablosu

T

|

Q(n)

|

Q(n+1)

|

J

|

K

|

0

|

0

|

0

|

0

|

X

|

0

|

1

|

1

|

X

|

0

|

1

|

0

|

1

|

1

|

X

|

1

|

1

|

0

|

X

|

1

|

Bloklayan atamalar kodlandığı sırada

gerçekleştirilirler, bundan dolayı bunlar ardışıldır. Şuanki ifade

gerçekleştirilene kadar bir sonraki ifade bloklanır, bunlara bloklayan ifadeler

denir. Atamalar “=” sembolüyle yapılır.

Bloklamayan ifadeler paralel olarak

gerçekleştirilir. Bir sonraki ifadenin gerçekleştirilmesi mevcut ifadenin gerçeklemesini

beklemez yani mevcut ifade bir sonraki ifadeyi tıkamaz, Bu atama türüne bloklamayan ifade

denir. Atama <= sembolüyle yapılır.

|

| Bloklayan Atama Simülasyonu |

module D_Flip_Flop_Blok(Q, D, Clock);

input D, Clock;

output [0:1] Q ;

reg [0:1] Q;

always@(posedge Clock)

begin

Q[0]=D;

Q[1]=Q[0];

end

endmodule

|

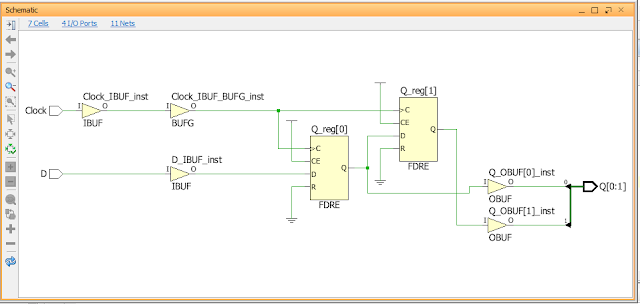

| Bloklamayan Atama Simülasyonu |

module D_Flip_Flop_NonBlok(Q, D, Clock);

input D, Clock;

output [0:1] Q ;

reg [0:1] Q;

always@(posedge Clock)

begin

Q[0]<=D;

Q[1]<=Q[0];

end

endmodule

Bir sonraki yazımda görüşmek üzere...